教育培训

教育培训

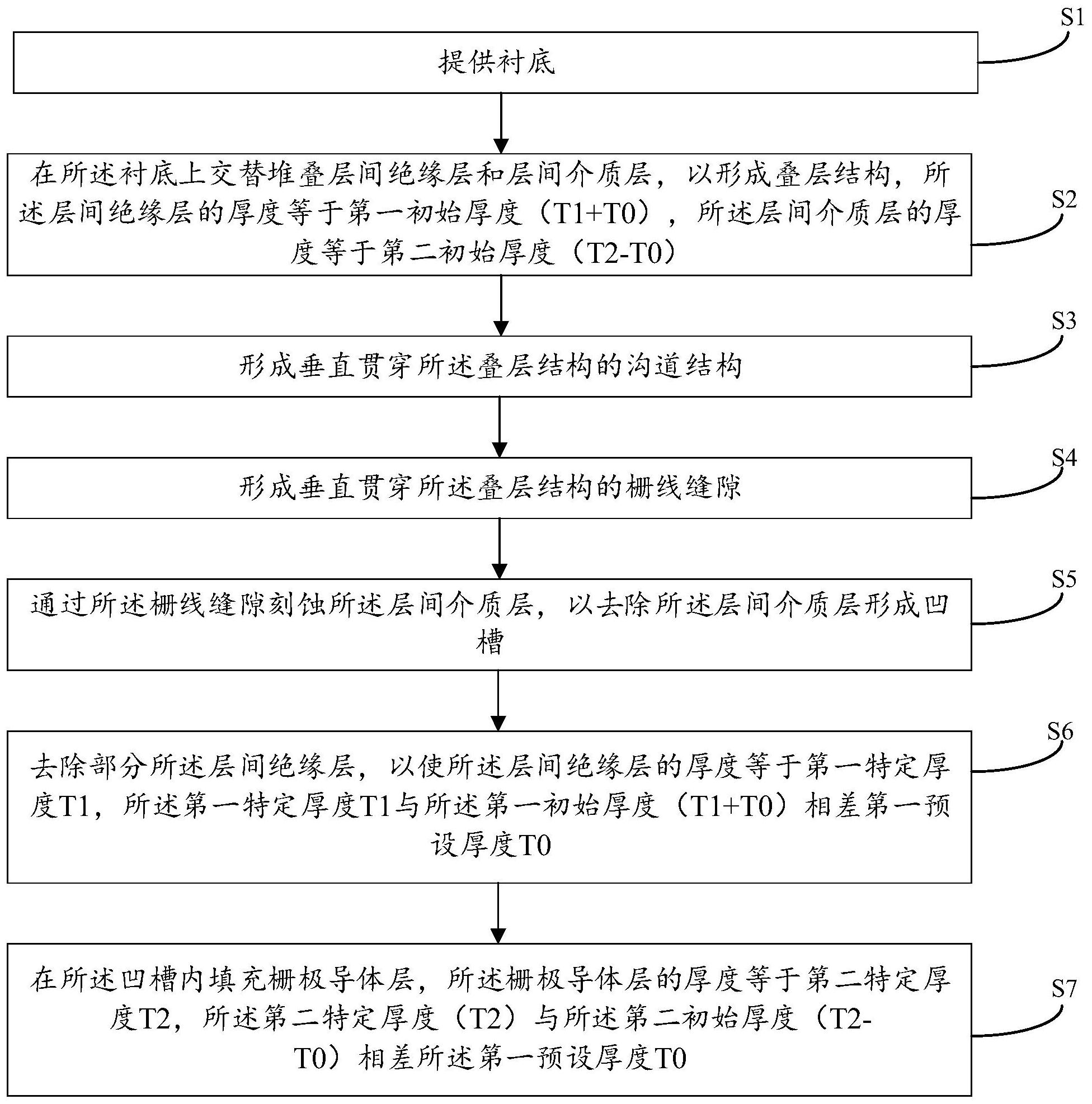

| 申请号 | CN202110612944.4 | 申请日 | 2021-06-02 |

| 申请公布号 | CN113345911A | 申请公布日 | 2021-09-03 |

| 授权公布号 | CN113345911B | 授权公告日 | 2023-12-15 |

| 分类号 | H10B43/35;H10B43/27;H10B41/35;H10B41/27 | ||

| 分类 | 基本电气元件; | ||

| 申请人名称 | 长江存储科技有限责任公司 | ||

| 申请人地址 | 湖北省武汉市武汉东湖新技术开发区未来三路88号 | ||