教育培训

教育培训

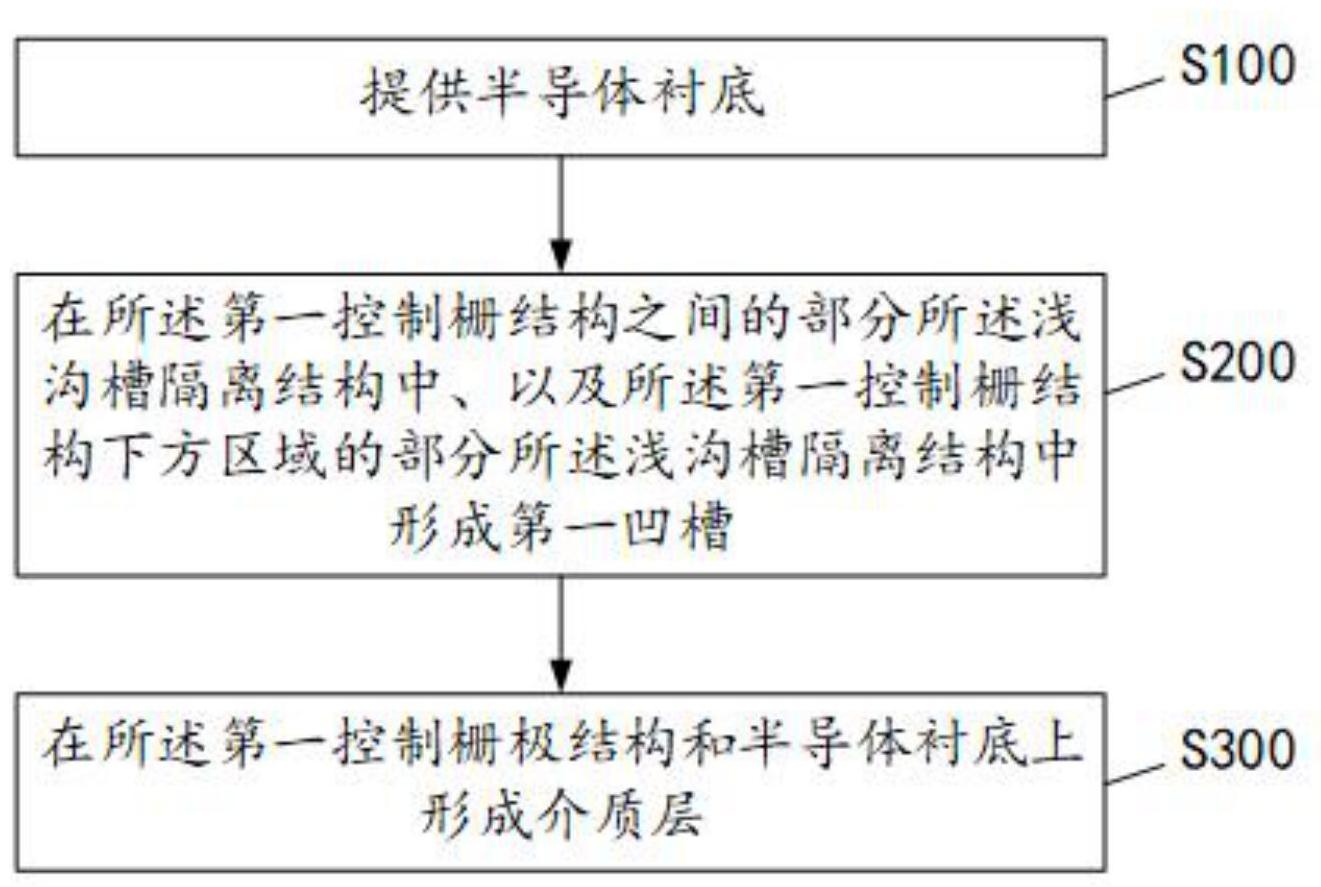

| 申请号 | CN202010291020.4 | 申请日 | 2020-04-14 |

| 申请公布号 | CN113540105A | 申请公布日 | 2021-10-22 |

| 授权公布号 | CN113540105B | 授权公告日 | 2023-11-03 |

| 分类号 | H10B41/35;H10B41/50;H10B41/27 | ||

| 分类 | 基本电气元件; | ||

| 申请人名称 | 中芯国际集成电路制造(上海)有限公司 | ||

| 申请人地址 | 上海市浦东新区中国(上海)自由贸易试验区张江路18号 | ||