教育培训

教育培训

| 申请号 | CN201710516715.6 | 申请日 | 2017-06-29 |

| 申请公布号 | CN107329867A | 申请公布日 | 2017-11-07 |

| 授权公布号 | CN107329867B | 授权公告日 | 2021-05-28 |

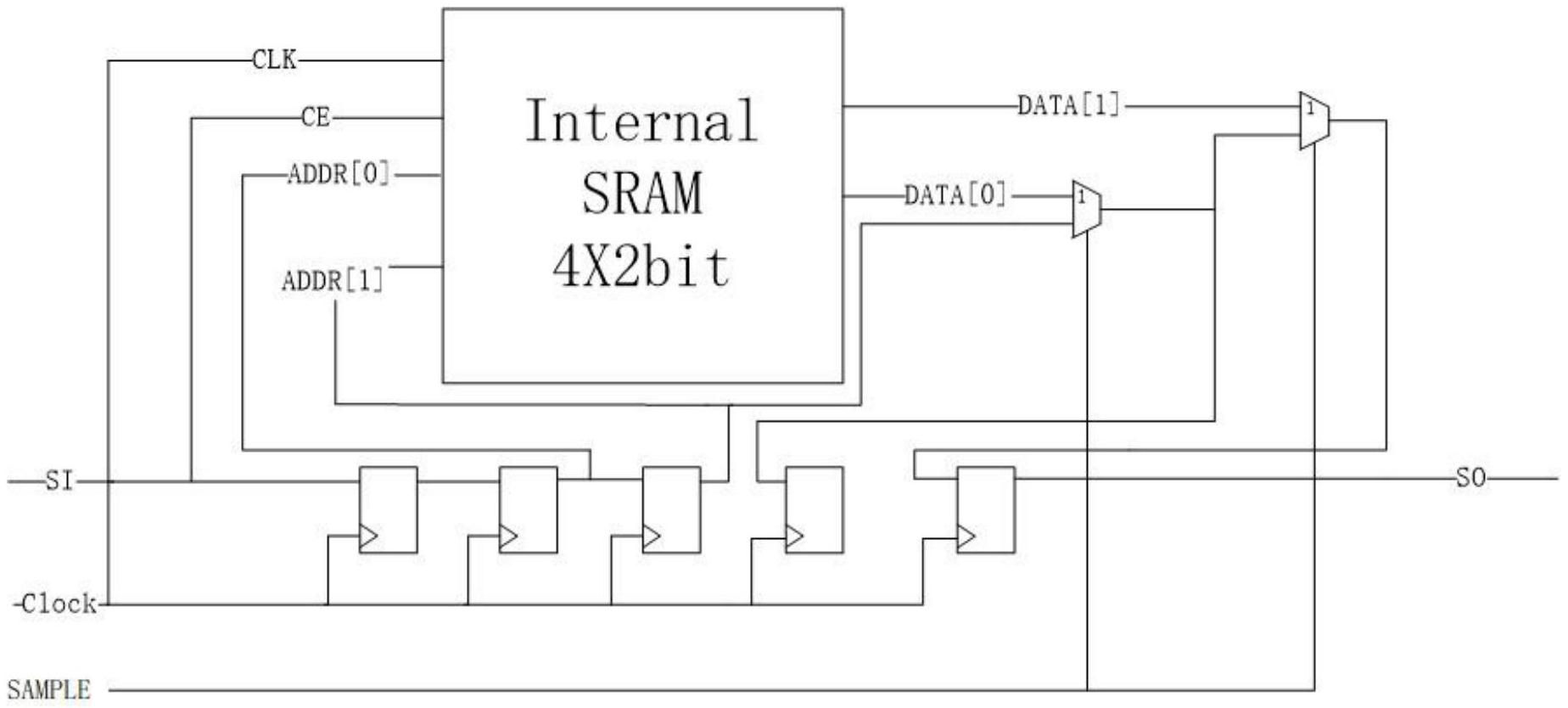

| 分类号 | G06F11/22;G06F11/263 | ||

| 分类 | 计算;推算;计数; | ||

| 申请人名称 | 记忆科技(深圳)有限公司 | ||

| 申请人地址 | 广东省深圳市南山区蛇口街道蛇口后海大道东角头厂房D14/F、D24/F、D15/F | ||