教育培训

教育培训

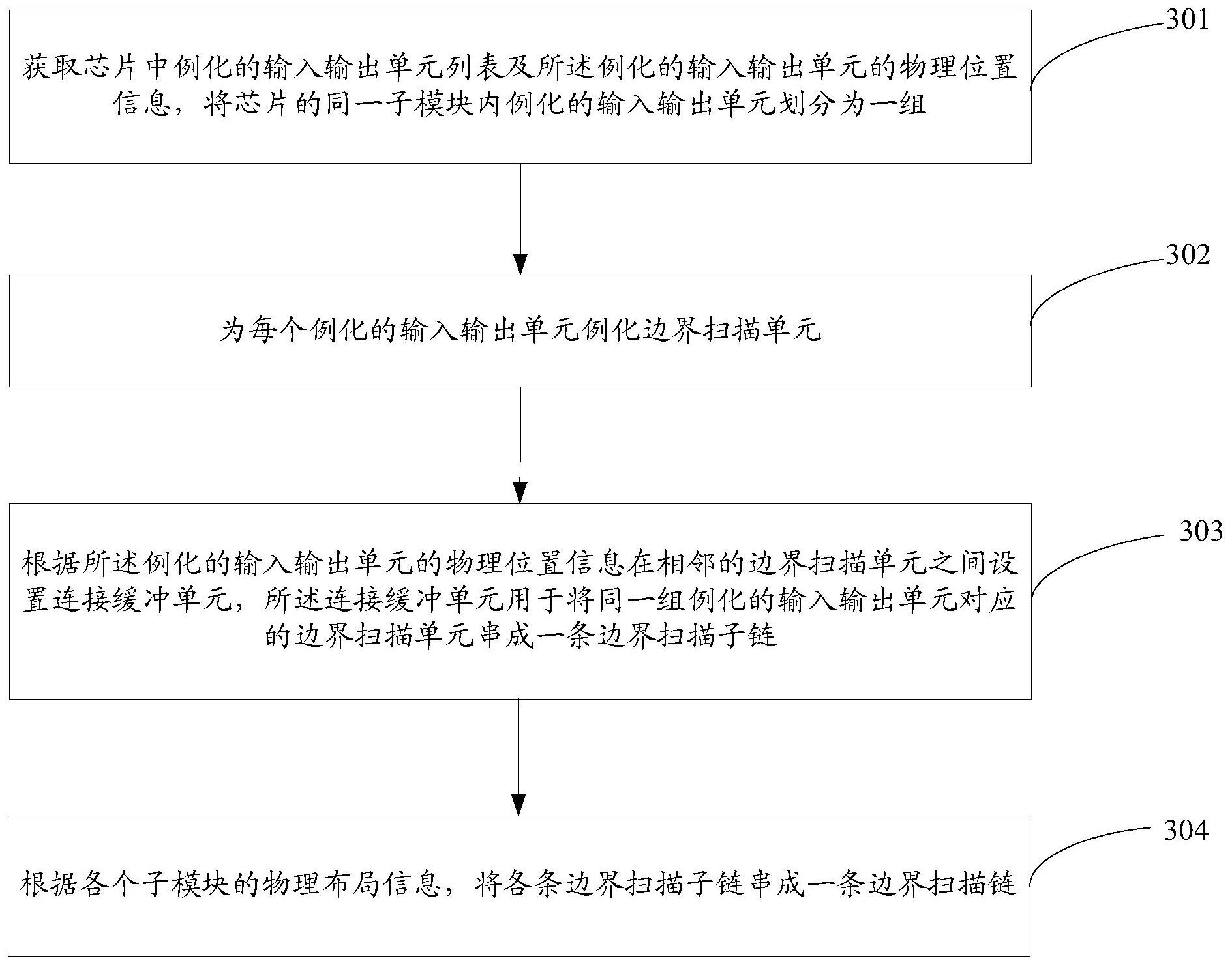

| 申请号 | CN201710720248.9 | 申请日 | 2017-08-21 |

| 申请公布号 | CN109426671A | 申请公布日 | 2019-03-05 |

| 授权公布号 | CN109426671B | 授权公告日 | 2022-10-14 |

| 分类号 | G06F30/398ICN103487747A,2014.01.01;US2005210349A1,2005.09.22;JP2005300217A,2005.10.27;US2008141086A1,2008.06.12;US2005166109A1,2005.07.28HBShashidhara等.BoardlevelJTAG/boundaryscantestsolution.《InternationalConferenceonCircuits,Communication,ControlandComp | ||

| 分类 | 计算;推算;计数; | ||

| 申请人名称 | 深圳市中兴微电子技术有限公司 | ||

| 申请人地址 | 广东省深圳市南山区西丽街道留仙大道中兴工业园 | ||