教育培训

教育培训

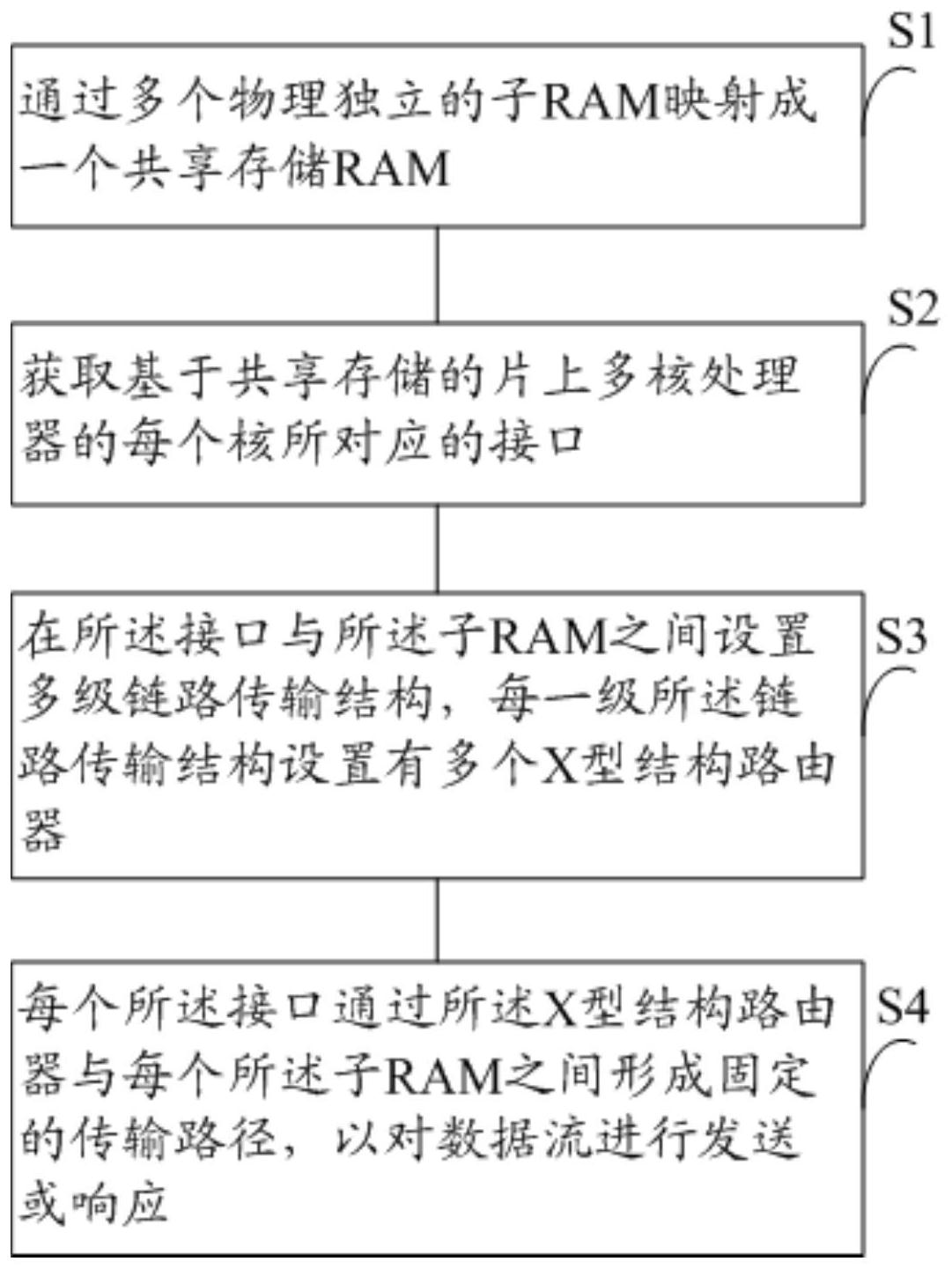

| 申请号 | CN202010345579.0 | 申请日 | 2020-04-27 |

| 申请公布号 | CN111597138A | 申请公布日 | 2020-08-28 |

| 授权公布号 | CN111597138B | 授权公告日 | 2024-02-13 |

| 分类号 | G06F15/167;G06F15/173;CN101477512A,2009.07.08;CN105468568A,2016.04.06;CN107852379A,2018.03.27;CN110908929A,2020.03.24;CN1622516A,2005.06.01;US2017220499A1,2017.08.03王一拙;左琦;计卫星;王小军;石峰;.访存敏感的增量式MPSoC应用映射.计算机研究与发展.2015,(05),206-217.;OrestisLiolis.Quantum-dot | ||

| 分类 | 计算;推算;计数; | ||

| 申请人名称 | 科大讯飞股份有限公司 | ||

| 申请人地址 | 安徽省合肥市高新开发区望江西路666号 | ||